## **MARCH** 2016

www.edn-europe.com

**DIGIKEY.COM/SCHEMEIT**

FREE Schematic, block or icon diagramming tool for electronic engineers

Salemetl

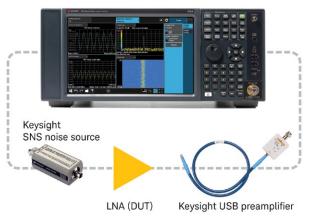

## Keysight Technologies X-Series Measurement Application Improve your noise figure

measurements.

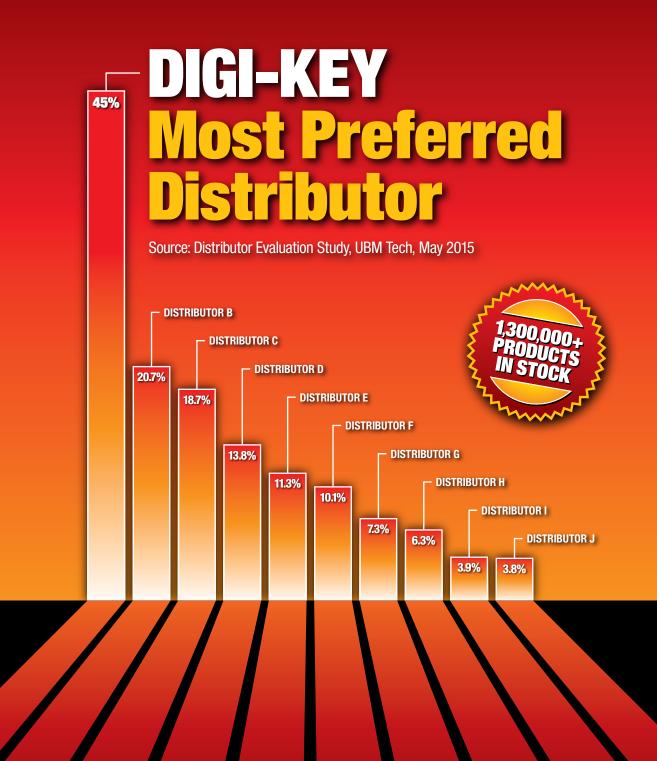

#### 4.8 MILLION PARTS ONLINE

OVER 650 INDUSTRY-LEADING SUPPLIERS

100% AUTHORIZED DISTRIBUTOR

#### FIND CONTACT AND ORDERING INFORMATION FOR YOUR REGION AT DIGIKEY.COM/EUROPE

\*A shipping charge of €18.00 (£12.00) will be billed on all orders of less than €65.00 (£50.00). All orders are shipped via UPS for delivery within 1-3 days (dependent on final destination). No handling fees. All prices are in euro and British pound sterling. If excessive weight or unique circumstances require deviation from this charge, customers will be contacted prior to shipping order. Digi-Key is an authorized distributor for al supplier partners. New product added daily. © 2016 Digi-Key Electronics, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

## COVER

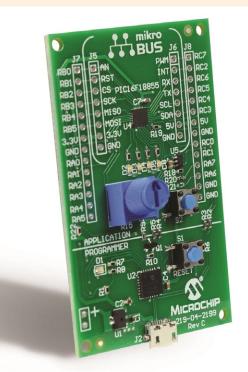

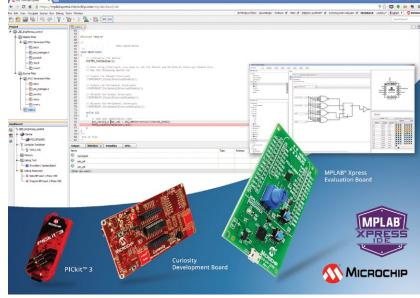

## Microchip opts for cloud-based IDE to attract PIC 'newbies'

icrochip Technology recently gave away thousands of these MPLAB Xpress Evaluation Boards as part of its launch of a cloud-based design environment for PIC microcontrollers. The programme is, in part, intended to introduce the architecture to non-PIC aficionados from hobbyist through to professional, and the software promises that you can do real development work, without even the need to register – more on page 17 of this issue.

## **FEATUREARTICLES**

- 18 Three ways to reduce uncertainty and improve noise figure measurements (sponsored article) by Cherisa Kmetovicz, Keysight Technologies

- 20 Reducing test time and costs with new compression technology by Mike Vachon, Software Engineering Group Director, Cadence

- 23 Paying down technical debt by John Paliotta, Vector Software

- 24 Using communications semiconductors to cook better burgers by Robin Wesson, Ampleon

- 28 Attaining functional safety in MCU-based designs by Hoiman Low, Texas Instruments

- **31 Optimising display image quality and power consumption by varying frame rate** *by Gi Young Lee, Exar*

- 33 Don't over-constrain in formal property verification (FPV) flows by Anders Nordstrom, Synopsys

#### **ONLINE THIS MONTH**

Toolbox for MATLAB enables faster and more robust WLAN design

Implementing an IoT end-point SoC platform with minimal engineering resources

## **EDN's columns**

#### 4 EDN.comment

Safe and Secure

6 Pulse

Raspberry Pi 3 adds connectivity; ARM+FPGA: module hosts Altera Cyclone SoC; EV charger packs 2.6 kW/l, >97% efficiency; Free tools to develop Linux on STM32; Automated filter design package offers intuitive, graphical approach; Free, cloud-based development platform for PIC; Untethered 3D dead-reckoning; Rohde & Schwarz 2 GHz scope offers linked multi-domain views

22 Eye on Standards

It's Not Jitter, It's Noise by Ransom Stephens

27 EDA: Synthesis

New generation of physical RTL synthesis improves quality-of-results by Arvind Narayanan, Mentor Graphics

44 Embedded Systems

Connected devices – security starts with software design

by Mark Warren, Perforce Software

#### 39 Product Roundup

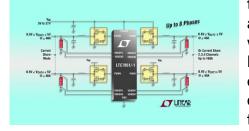

4G LTE M2M modem; Capacitive multi-touch uses metal mesh; Multiphase step-down DC/DC up to 260A; Fast LVDS isolators eliminate de-serialising; SBC with Xilinx' SDSoC for hardware IP acceleration; Renesas develops Synergy platform for IoT; Full Bluetooth LE node in 8x8x1mm; IoT sensor-to-cloud from ADI; Highefficiency 15-W wireless power

- **35** Design Ideas

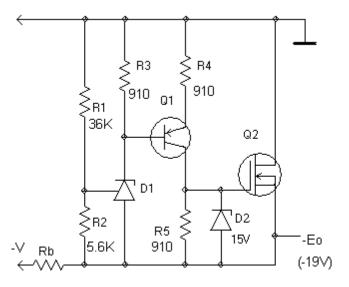

- 36 Active load handles high voltages

- 37 Shunt circuit clips large transients or regulates voltage

ttending the embedded world exhibition in Rebruary, I heard – you will not be surprised to learn - many presentations on silicon, software and systems for the coming era of connected devices. Yes; the Internet of Things. And as part of that, much content on providing the necessary security aspects. At least, as the IoT bandwagon rolls on, the industry recognises that there is a security issue; and it is energetically engaged in providing all of the component parts needed to embed security. Microcontrollers for connected-device roles now routinely come with on-board cryptography engines; secure operating systems migrate from the bigsystems world to the coin-cell-powered space; IoT 'back-office' infrastructure offerings boast their levels of protection against intrusion. All the components you might need are already out there.

Why, therefore, am I not entirely convinced? It is the very complexity of providing an end-to-end secure context for the IoT data traffic: and the need for it to be, in that favourite term of the marketer, "seamless". IoT systems will present – we will all have to take on board the jargon – a very large attack surface. Every aspect of a system will have to have security embedded from the outset, will have to work together correctly, will not contain code of doubtful provenance re-used from older projects – the list goes on.

The environment has also changed. The rule-ofthumb metric for assessing security was once; a system is safe if the effort to attack it significantly

## **SAFE AND SECURE**

outweighs the gains the attacker might make. That is no longer the case. There is a world of hackers that will delight in applying virtually unlimited effort to penetrating the barriers around any product that claims to be secure, for no more gain than the kudos of having done so. And the "pro" hackers have not gone away.

The risks are high. A handful of high-profile cases of data loss could damage perceptions of the entire connected-device project. Even without that happening, on the consumer side the buying public will have to be convinced that the benefits to be had from connectivity (connected-ness?) are worth the risks. I heard one industry executive attending embedded world express it like this (he named a brand of connected domestic heating controller, and an Internet services provider, which I should perhaps not quote), "Am I going to install a device that uploads data to the net, and stores it whoknows-where - even if the provider assures me that data is safe – that has embedded in it, information about when I'm at home and when my house is unattended? Just so I can turn up the heating from my phone? I don't think so." Insiders are often the hardest to sell to, but the concern is completely understandable.

The range of product offerings for IoT design is also coming to reflect the fact that this is a different context. We are all familiar with the regular update cycle that it takes to maintain protection against malware on our desktop and mobile computing platforms. An embedded operating system may be tiny compared, say, to Windows. But applying patches to it will be a challenging problem: the device will have to be designed with sufficient resources to support an update cycle (enough memory to store new and fall-back versions, for example) plus routines sufficiently robust to withstand attack before, during and after an update. And patches will be needed in products that are – as we are constantly told – intended to operate unattended for years or even decades. The intention is that IoT devices proliferate in millions; how to ensure that essential updates propagate to every active unit?

More insidious than the vulnerability of the IoT product itself, is the potential for it to act as a gateway. It is, after all, 'connected', and in its long expected life, it may come to be connected in ways not envisaged by the original design team. It may be an unduly pessimistic point of view, but considering the multiple challenges of making these new product concepts secure, and taking into account the fact that even with the best intentions. engineering tends to learn and be shaped by the occasional failure - we should be prepared for some disasters. If the PC and commercial software experience is any sort of guide, we should also be prepared for future in which the security task is never finished. Devices with a selling price of a handful of euros, pounds or dollars, that have a maintenance burden lasting decades: that is the reality of what we are signing up to.

## Become your company's most valuable player.

#### Elevate your status with Keysight's InfiniiVision oscilloscopes.

Get your projects on the fast track with features such as zone triggering, built-in analysis software and super-fast waveform update rates. Plus Keysight has a team of experts ready and available to help you overcome any test and measurement obstacles. You already have the talent, and with Keysight you have the tools you need to become your company's MVP.

| Keysight InfiniiVision<br>oscilloscopes | 2000 X-Series                                                                         | 3000T X-Series | 4000 X-Series   | 6000 X-Series |  |

|-----------------------------------------|---------------------------------------------------------------------------------------|----------------|-----------------|---------------|--|

| Bandwidth                               | 70 MHz-200 MHz                                                                        | 100 MHz–1 GHz  | 200 MHz-1.5 GHz | 1 GHz-6 GHz   |  |

| Instrument integration                  | Arbitrary waveform generator, digital voltmeter, protocol analyzer, FFT, counter, MSO |                |                 |               |  |

Ready to achieve MVP status? Go to the Scopes Learning Centre: www.keysight.com/find/OscilloscopeMVP

Unlocking Measurement Insights

© Keysight Technologies, Inc. 2016

# DUSE

#### Raspberry Pi 3 steps up performance, adds connectivity

The Raspberry Pi Foundation, with distributors RS Components (Electrocomponents) and Farnell element14 have introduced the latest version of the single-board computer; it has a 50% increase in processing power relative to Raspberry Pi 2; and adds onboard wireless connectivity for WiFi and Bluetooth LE. All of the updates have been achieved while maintaining the original price point of \$35. The processor upgrade is to a Quadcore Broadcom BCM2837 64bit ARMv8 processor (running an ARMv7 operating system) at [up to] 1.20 GHz, a significant increase from 900 MHz available with the Raspberry Pi 2. The Broadcom chip uses the Cortex-A53 core. Eben Upton, CEO of Raspberry Pi Trading (which is the licensing body controlling Raspberry Pi) and originator of the Raspberry Pi Foundation, said that the latest version continues the Foundations's charitable objectives of raising enthusiasm for computer science and engineering among

the young, while the availability of on-board Bluetooth LE (and WiFi) firmly positions it as an IoT hub. Referring to the range of spinoff products that has arisen for embedded computing use, the organisation is, "heading towards Compute Module 3", for release

at a later time. In the context of its educational role, Upton says of the Pi 3, "It crosses the line from [possibly being considered as] a toy, to being a full PC...

ne [posbeing dered toy, ing a C...

it was never intended to be just a 'worthy' platform."

For element14, a spokesman commented on the Raspberry Pi "customisation" offering that was introduced four months previously; the distributor has seen around 300 'opportunities' of which several are approaching realisation. Most projects so far have involved relatively minor changes to the basic platform, around configuring interfaces and peripherals, and cost-reduction. Batch sizes for possible variants start at 5000

units, upwards. The added on-board connectivity of the model 3 is cited as the largest single gain for embedded users. element14 is adding to its offering of associ-

ated products, to include a PiFace interface board, a starter kit (for IoT-class projects) that has been designed with EnOcean and that will use the IBM Bluemix cloud service; an uprated, 2.5A power supply that will power the Pi and any additional boards from a single source; a new moulded case; and a 16 GB NOOBS (New Out Of the Box Software) memory card. RS Components adds the detail that the connectivity comes from a BCM43438 combo device, which provides 802.11b/g/n wireless LAN, Bluetooth Classic and Bluetooth Low Energy. The main SoC BCM2837 integrates a dual-core VideoCore IV multimedia coprocessor, which provides; 1.2G pixels/sec of fill rate, 1.8 Gtexel/sec of texturing rate; 29 GFLOPs of shader compute throughput; OpenGL ES 1.1/2.0 support; 1080p60 hardware video decoding; 1080p30 hardware video encoding; and a hardware image sensor pipeline. This, Upton comments, represents a small increment of GPU power over the version 2, while the overall CPU performance (over a mixed, general purpose instruction benchmark) is 10x that of the original Pi and

50% up on the Pi 2.

## ARM+FPGA: module hosts Altera Cyclone SoC, offers high I/O count

Enclustra's (Zurich, Switzerland) Mercury+ SA2 is an Altera Cyclone V SoCbased module with over 250 I/Os; the Altera chip gives it a high-performance processor system and many standard interfaces: it is equipped to handle even the most demanding of applications.

The module combines an ARM dual-core Cortex A9 processor with a

28 nm FPGA fabric, all in a package measuring just 74 x 54 mm. The module's 258 user I/Os, 2 GByte DDR3L SDRAM and 64 MByte quad SPI flash combine to form a high-performance processing unit. Multiple interfacing options are also available: 9 MGTs with a data transfer rate of up to 6 Gbps, PCle Gen1/Gen2 x4, Gigabit Ethernet, dual Fast Ethernet, USB 3.0 and USB 2.0. The module is available in both commercial and industrial temperature range, and needs just a single

5-15 V supply for operation.

Enclustra also offers a comprehensive ecosystem for the SA2, offering all required hardware, software and support materials. The Mercury+ PE1 base board is a complete development platform for the SA2; detailed documentation and reference designs are available, in addition to the user manual,

schema, a 3D-model, PCB footprint and differential I/O length tables.

#### Authorised Distributor

NEW IN Stock

## **Development Tools**

Learn More

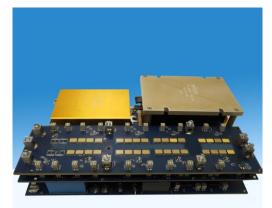

#### Electric-vehicle charger packs 2.6 kW/I, >97% efficiency, with GaN switches

A utomotive electronics company Hella, in collaboration with gallium nitride semiconductor maker GaN Systems and charging technology researchers at Kettering University's Advanced Power Electronics Lab (Flint, Michigan, USA), have developed a Level-2 electric vehicle (EV) charger prototype with efficiencies exceeding 97% at an "unprecedented" 2.6 kW/l power density.

Prior to this achievement, Level-2 EV chargers – according to the collaborators – reached maximum efficiencies of 94%. Using GaN Systems' 60A, 650 V GS66516T switches in a two-stage archi-

tecture, the Kettering University research team, led by Associate

International Exhibition and Conference

for Power Electronics, Intelligent Motion,

Nuremberg, 10 – 12 May 2016

**Renewable Energy and Energy Management**

pcim

**EUROPE**

Professor of Electrical Engineering, Dr. Kevin Bai, were able to increase the wall-to-battery efficiency to more than 3% greater

More information at +49 711 61946-0 pcim@mesago.com or pcim-europe.com

than previously obtained. Dr. Bai and his team are known for collaborating with companies to help advance their charging technology. Commenting on the importance of this development, Dr. Bai said, "The switching performance we observed with the GaN Systems' parts was marvellous. Using these devices our power electronics exhibited a power density greater than 2.6 kW/l. This is a significant milestone with important implications for charging electric vehicles, among other charging applications." Dr. Bai characterised this development as

a 'game changer' for the EV charging industry.

#### Free tools to develop Linux on STM32 MCUs

STMicroelectronics has extended its "design free" tool support to both Linux and Windows platforms, for microcontrollers in the STM32 architecture. Until now, however, (says ST) most development tools for embedded computing have been available only for Windows.

The STM32CubeMX configurator and initialisation tool and the System Workbench for STM32, an Integrated Development Environment (IDE) created by French company Ac6

Tools, supported by the openSTM32. org community, and available at www.st.com/sw-4stm32, are now both available to run on Linux OS.

Develop free of charge under Linux for STM32 MCUs

ST's latest move means Linux users can now start their own embedded projects on STM32 devices, free of charge, without leaving their favourite desktop environment. Users, ST adds, can now benefit from free software for configuring microcontrollers and developing and debugging code, together with manufacturersupported low-cost evaluation boards, allowing greater focus on product development. Tools installation is very easy and fast, which

contrasts with established practice in the Linux world, where users often have to create or adapt their own tools with minimal support. System Work-

develop software debug for ARM-based embedded systems, designed to run directly on-chip) community project. Each of these tools can be used in conjunction with ST's low-cost development hardware including STM32 Nucleo boards.

open project to

bench for STM32 supports the ST-LINK/V2 debugging tool under Linux through an adapted version of the OpenOCD (OpenOCD: Open On-Chip Debug, a free and

Discovery kits, and Evaluation boards, as well as microcontroller firmware within the STM32Cube embedded-software packages or Standard Periph-

USB TYPE-C CONNECTOR Mid-Mount Hybrid Receptacle With enhanced EMI and board retention features this slim profile connector is small enough for handheld devices yet robust enough for industrial applications.

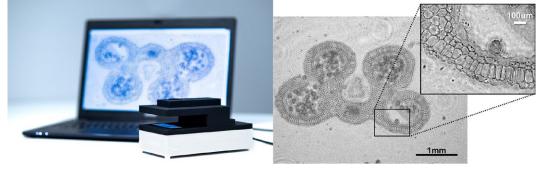

## Compact lens-less digital microscope – evaluation kit available

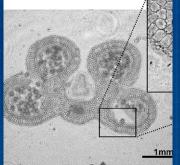

DN Europe first reported on the work on lens-free microscopy at Belgian research centre imec in 2014. Now, the technique has been packaged into a demonstration and evaluation kit. Able to provide a large field-ofview and live imaging at micrometer resolution, imec's on-chip lens-free microscope can be integrated into life sciences and biotech tools, targeting multiple applications such as label-free cell monitoring, automated cell culturing, or automated highthroughput microscopy. The principle behind lens-free imaging is based on in-line holography capturing the interference between

an illuminating wavefront and the diffraction of an object. Selection of field of view; of magnification; and of plane of focus; all become software operations.

Compared to conventional optical microscopes, lens-free digital microscopy removes the need for expensive and bulky optical lens components to acquire and visualise microscopy images. In a lens-free digital microscope, images are captured on a CMOS image sensor, and digitally reconstructed using software. Imec's lens-free microscope features a comparable micrometer-scale accuracy as traditional optical microscopes, while being

much smaller and less expensive; the microscope captures a larger field-of-view and enables a full-resolution selection to be achieved across a much wider field in one shot, enabling shorter sample processing times. The lens-free microscope paves the way to new applications with living cells and tissues.

"Imec's lens free imaging solution is now available as a full, ready-to-use demo kit evaluation system including a light source, image sensor, control and readout electronics and a software interface," stated Jerome Baron, business development manager of integrated vision systems at imec. "Companies can use it to try out their own applications, supported by our engineers to fine-tune the hardware and software and customise the systems toward their exact application requirements."

**Connecting Global Competence**

#### **Business meets technology**

Join your community and benefit from

- Networking—Where manufacturers and end users come together.

- Knowledge transfer—Research that inspires product ideas.

- Industry orientation—State of the art technology that reveals market opportunities.

This is the place where printed electronics come to life.

#### Exhibition: April 6–7, 2016 Conference: April 5–7, 2016

Messe München, Germany

#### Rohde & Schwarz puts spotlight on cybersecurity, adds new division

The communications and T&M company is to set up a specialist group that combines its IT and network security subsidiaries as 'Rohde & Schwarz Cybersecurity'. Rohde & Schwarz Cybersecurity will apply a new securityby-design technological concept to deliver proactive protection against outside attacks; the company has taken this approach to safeguarding data and communications in times of global networking, and is increasing its involvement in this future market. Rohde & Schwarz has been active in the field of IT security for over 20 years. In 2014 and 2015, the group enhanced its knowhow by acquiring **Adyton GmbH**, **gateprotect GmbH** and **Sirrix AG**. Long-standing subsidiaries **ipoque GmbH** and **Rohde & Schwarz SIT GmbH** will continue to contribute to the portfolio with their expertise and solutions. As part of the consolidation, Rohde & Schwarz SIT will be reorganised: its Stuttgart office will focus on its core business of radiocommunications encryption solutions. The end-to-end encryption and network security product groups will remain in Berlin. They will be integrated into Rohde & Schwarz Cybersecurity GmbH, which will have a total of nearly 400 employees at six locations in Germany. Rohde & Schwarz Cybersecurity offers a wide range of technologically leading solutions for information and network security. Highly secure encryption solutions, nextgeneration firewalls and software for network analysis and endpoint security protect enterprises and public institutions worldwide against espionage and cyberattacks. Security solutions range from compact, all-in-one products to customised solutions for critical infrastructures. The development of trusted IT solutions focuses on the new security-by-design technological concept for preventing external attacks proactively instead of reactively.

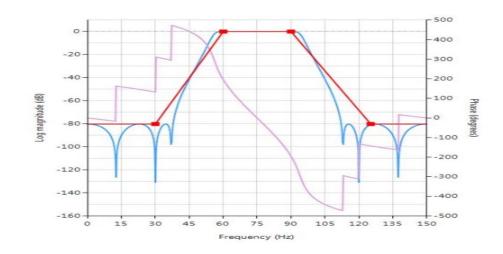

#### Automated filter design package offers intuitive, graphical approach

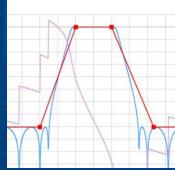

Advanced Solutions Nederland has formally released version 3.0 of its ASN Digital Filter Designer. The company says that the package, for IIR and FIR filter design, offers an intuitive route to implementing digital filters that represents the first significant advance in this class of tools for many years. The tool is a Windows-based package that assists

with design of filters, primarily for implementation on processor targets, but also supporting floating point desktop algorithm development: work in this space has focussed on biomedical applications. ASN contends that, although existing design tools in the market can produce good results, their roots often date back some way (decades, in some cases), they were conceived for use by an "expert" level of filter designer and considerable specialist expertise is needed to reach those results. ASN Digital Filter Designer has been structured to use an intuitive input approach that largely dispenses with entering parameters in text fields. Rather, it uses a GUI-based methodology in which the user draws the desired filter response (for classical filter configurations). For those classic designs, the tool will work directly from a graphical input to establish the necessary technical specifications for both IIR and FIR filters. Alternatively, the user can create customised designs by entering specifications as simple symbolic mathematical expressions and then interactively experiment-

ing with settings. The symbolic math scripting language allows exploration of complex designs.

The software supports detailed time and frequency domain analysis and a pole/zero editor to fine-tune a design. Outputs include full documentation and reports, and filter coefficients can be exported other environments (Matlab, etc.) for further analysis or development. IIR filter design can proceed with classical forms in lowpass, highpass, bandpass and bandstop configurations in Butterworth, Chebyshev Type I, Chebyshev Type II or Elliptic types, with filter orders of up to 100 (in the 'professional' version of the tool) supported. FIR (finite impulse response) filter design is implemented via the Parks-McClellan algorithm, and allows for the design of lowpass, highpass, bandpass, bandstop, multiband, Hilbert transformer, and dif-

ferentiator filters with orders up to 500.

#### Mentor proposes Open Manufacturing Language for PCB assembly

entor Graphics has launched the Open Manufacturing Language (OML) initiative that directly addresses what it terms the longstanding need and urgent calls from the industry for a printed circuit board (PCB) assemblyspecific "Internet of Manufacturing", "Industry 4.0" solution. For the first time – Mentor says – IT teams, solution providers, and equipment providers can integrate shop-floor data to create or enhance added-value manufacturing execution solutions based on a single, normalised, vendor-neutral communication interface. This minimises development and support effort while ensuring optimum data accuracy, timeliness and completeness.

Use of the OML standard supports numerous industry needs and challenges including the practical realisation of the Internet of Manufacturing, Industry 4.0 and Smart Factory 1.0 concepts, as well as the automated collection of full traceability data including routing and compliance enforcement. OML creates an operational hierarchy through which neutralised information is exchanged between manufacturing processes. This includes detail of any shop-floor event in the areas of process performance, materials setup and consumption, traceability, process results and parameters, process control (poka-yoke), and quality information from test, inspection and repair processes, both automated and manual. OML resolves numerous issues in automated and manual processes that previous formats could not address. The standard will be available through an open community on www.OMLcommunity.com. The community will provide support and management of new revisions. Membership of the community is now open for end-users, machine vendors, and other interested parties by registering at the website where a free download of the full documentation and samples are available.

#### Untethered 3D dead-reckoning bridges gaps in automotive location fixes

-blox' NEO-M8U is presented as the first Untethered 3D Dead Reckoning (UDR) module; combining multi-GNSS (GPS, GLONASS, BeiDou, Galileo) with an onboard 3D gyro/accelerometer, NEO-M8U provides accurate positioning even where GNSS signals are weak or not available. It achieves this without any connection to the vehicle other than power.

The u-blox NEO-M8U module

provides superior multipath sup-

pression,

which im-

proves posi-

tion accuracy

even in tough

environments.

such as urban

canyons, tun-

nels, or park-

ing garages. For example,

in London's

city centre area, NEO-M8U is

typically three times more accurate than a traditional GNSS receiver. NEO-M8U offers instantaneous position immediately after powerup, without the need to wait for a first fix as with regular GNSS receivers.

Simplifying product development and installation, NEO-M8U looks and behaves just like a regular GNSS receiver and does not require any special mounting or connection to the vehicle. With intelligent sensing and continuous self-calibration, NEO-M8U

can be installed in the vehicle in any orientation.

#### **Quad SPI FRAM at 4Mbit capacity**

Fujitsu's ferroelectric RAM offers high speed non-volatile memory for networking, industrial computing and HMI applications. The company presents the MB85RQ4ML as the first-available Quad SPI FRAM device. It integrates 4 Mbit FRAM (Ferroelectric Random Access Memory) and Quad SPI interface. By using 4 bi-directional I/O pins, the Quad SPI FRAM device can reach a data transfer rate of 54 MByte per second at an operating frequency of 108 MHz. In this respect, the memory is over four times as fast as Fujitsu's existing parallel 4Mbit

FRAM device and outperforms 45 nsec parallel SRAM. MB85RQ4ML comes in an SOP-16 package. In comparison to the company's parallel devices of the same density, which are housed in TSOP-44 or TSOP-48 packages, it achieves a package size reduction of at least 50% as well as a pin count reduction of 60%. Besides its high speed, The device offers the

usual FRAM characteristics such as non-volatility and high endurance of 10 trillion read/ write cycles. Since power is not required to retain the data written in the memory, MB85RQ4ML can replace battery backed-up SRAMs. While the conventional memory architecture of embedded systems consists of a RAM and a nonvolatile memory, it can, in many applications, replace both kinds of memory technologies and offer a unified memory technology in one chip.

MB85RQ4ML operates at a voltage range of 1.7 – 1.95V. As well

as Quad SPI, single SPI interface is supported.

#### Hardware cryptographic acceleration and secure storage for TLS in IoT apps

A tmel has disclosed a hardware interface library for TLS stacks used in Internet of Things (IoT) edge node applications. Hardening is a method used for reducing security risks to a system by applying additional hardware security layers and eliminating vulnerable software.

Atmel's Hardware-TLS (HW-TLS) platform provides an API that allows TLS packages to use hardware key storage and cryptographic acceleration even in resource constrained edge node designs. HW-TLS is a comprehensive solution pre-loaded with unique keys and certificates de-

signed to eliminate the complexities of generating secure keys in the manufacturing supply chain. OpenSSL is a general-purpose cryptography library that provides an open-source implementation of the Secure Sockets Layer (SSL) and TLS protocols. wolfSSL is a cryptography library that provides lightweight, portable security solutions with a focus on speed and size. Atmel's ATECC508A-OpenS-SL and ATECC508A-wolfSSL are available for immediate download at their respective software distribution repositories, offering seamless adoption of more secure elements without disruption to the

developer workflow. Secure hardening for both OpenS-SL and wolfSSL is made possible with HW-TLS which allows those TLS software packages to interface seamlessly with the Atmel ATECC508A CryptoAuthentication co-processor. The ATECC508A provides protected key storage as well as hardware acceleration of Elliptic Curve Cryptography (ECC) cipher suites including mutual authentication (ECDSA) and Diffie-Hellman key agreement (ECDH). As such, HW-TLS allows developers to substantially harden Transport Layer Security (TLS), enhancing security for IoT-device and

cloud-service ecosystems. When used together, HW-TLS and the ATECC508A allow even extremely small, low-cost IoT nodes to implement strong cryptographic security. All private keys, certificates and other sensitive security data used for authentication are stored in secure hardware and protected against software, hardware and back-door attacks. In addition, the integrated ECC accelerators in the ATECC508A offload cryptographic code and math from the MCU allowing even a low end pro-

cessor to perform strong authentica-tion.

#### Rohde & Schwarz 2 GHz scope offers linked multi-domain views

Rohde & Schwarz' RTO2000, is a compact lab oscilloscope for multi-domain applications, displaying correlations between time, frequency, protocol and logic analysis measurement results. Via the analogue input channels, the user simultaneously sees the

signal in the time and frequency domain, and if desired, the spectrogram. Newly added functions such as peak list, max. hold detectors and the logarithmic display make frequency analysis more efficient.

A zone trigger enables the graphi-

cal separation of events in the time and frequency domain. Users can define up to eight zones of any shape. A trigger signal is activated when a signal either intersects or does not intersect the zone. This makes it easy to detect disturbances in the spectrum dur-

ing EMI debugging or to separate read/write cycles of storage media in the time domain.

It is the first oscilloscope in this class to offer a memory of up to 2 Gsample/sec. This is useful for the history function, which provides access to previously acquired

waveforms at any time. A trigger timestamp allows time correlation. Users can view all saved signals and analyse them with tools such as zoom, measurement, math and spectrum analysis functions. Signal processing in the ASIC and intelligent memory management ensure smooth handling of long pulse and protocol sequences. A high definition (HD) mode in-

creases the vertical resolution to up to 16 bits, making signal details visible. Achieved by signal processing, the high-resolution mode trades bandwidth for

increased detail. The HD mode

activates configurable lowpass filtering of the signal after the A/D converter. With one million waveforms per second, the R&S RTO2000 enables users to detect sporadic signal faults. The scope provides high-speed analysis even when histogram and mask functions are active. The R&S RTO2000 is available as a two or four channel model with a bandwidth of 600 MHz, 1 GHz, 2 GHz, 3 GHz or 4 GHz, priced from (approximately) €15,000 to €50,000

depending on configuration and bandwidth.

#### **3rd-generation IO-Link transceiver chip cuts power, package outline**

axim Integrated's MAX14827 enables intelligent sensors with reduced maintenance and increased uptime with continuous diagnostics and monitoring; it reduces power dissipation more than 50% over prior devices. Industrial systems designers, Maxim says, now have a robust **IOLink dual-channel transceiver** that dissipates the lowest heat in the smallest package; IO-Link sensors contribute to the 'Industry 4.0' trend by bringing intelligence and control down to the factory floor. Sensors are getting smaller and need to deliver more functionality,

while ensuring robust communications: power - says Maxim - is also critical because these sensors are small and it is difficult to dissipate heat. The MAX14827 dual-channel, 250 mA transceiver meets these requirements, while also integrating high-voltage functions commonly found in industrial sensors, including drivers and regulators. It features two ultra-low power drivers with active reverse-polarity protection to reduce downtime. For sensors that use a microcontroller. a SPI interface is available with extensive diagnostics. For IO-Link operation, a three-wire UART interface is provided, allowing interfacing to the microcontroller UART. A multiplexed UART/SPI option allows using one serial microcontroller interface for shared SPI and UART interfaces. The device includes on-board 3.3V and 5V linear regulators for low-noise analog/ logic supply rails.

Advantages include; a lower onresistance (RON): 2.5 Ohm Ron (typical) saves more than 50% power; the WLP package saves 60% space; a 65V Abs Max rating

Complete

rticle, here

enables flexible TVS protection selection.

#### Free, cloud-based development platform; entry to the world of PIC

Ay before the world learned that they were called 'makers', experimenters and product developers working around the boundary between the professional and semi-pro, even hobbyist, worlds could very often be found using Microchip PIC devices; now, the company has updated the entry path it offers to that group of users – and to the 'regular professional' sector that may not be

familiar with PICs – to take account of online, cloudbased trends.

The offering is called MPLAB Xpress IDE and Microchip says it provides the "easiest way to get started with PIC MCUs". It allows you do a considerable amount of work on a project without even registering ("no downloads, sign-in or setup required to start") It is an online, cloud-based development environment, the only one, Microchip says, with an integrated Code Configurator. You can pair it with hardware in the form of existing Microchip MPLAB boards, or with any PC plus the new MPLAB Xpress Evaluation Board – numbers of these (see below) are going to be in circulation via free hand-outs and if you miss out on those; for under \$10. The platform gives access to the entire family of PIC MCUs – initially, all 8-bit variants, with 16-bit parts to follow later in 2016. The 'first encounter' is a free login to

the site; that gives access to examples, code libraries and compilation – and to a code configurator (code generator) to set up a chosen target and its peripherals. A free account setup allows you to save work to the cloud, with the option of making work 'open' or visible to a community. Designers can, therefore, create an application, simulate, compile

code, programme and debug an MCU in this cloud-based toolset which inherits the most popular

features of the MPLAB X IDE. MPLAB Xpress offers a comprehensive feature set, including a library of Microchipvalidated code examples, interface to MPLAB Code Configurator (MCC) 3.0 for GUI-based MCU peripheral setup and automatic code generation, integrated MPLAB XC compilers, support for programmer/debugger hardware, and 10

GB of secure online storage with a myMicrochip account. Users can

easily migrate their projects to the full, downloadable MPLAB X IDE. A new MPLAB Xpress Community enables developers to share their code, design ideas and knowledge.

Cloud-based hardware development is supported by connecting any USB-enabled PC, laptop or tablet to tools such as the MPLAB **Xpress Evaluation Board**. This development board features an integrated programmer, a PIC16F18855 MCU and a mikro-BUS header for system expansion with MikroElektronika's more than 180 Click boards. The MPLAB Xpress IDE also supports Microchip's Curiosity Development Board (\$20.00), with integrated programmer and debugger, as well as expansion options for addon boards and external connectivity. The online IDE can be used with Microchip's PICkit 3 In-Circuit Debugger/Programmer (\$47.95), which provides programming and

debugging capabilities for over 1,000 PIC MCUs.

## **Critical Recording in Any Arena** When You Can't Afford to Miss a Beat!

Introducing Pentek's expanded line of Talon<sup>®</sup> COTS, rugged, portable and lab-based recorders. Built to capture wideband SIGINT, radar and communication signals right out-of-the-box:

TALON

- Analog RF/IF, 10 GbE, LVDS, sFPDP solutions

- Real-time sustained recording to 4 GB/sec

- Recording and playback operation

280

- Analog signal bandwidths to 1.6 GHz

- Shock and vibration resistant Solid State Drives

- GPS time and position stamping

- Hot-swappable storage to Windows<sup>®</sup> NTFS RAIDs

- Remote operation & multi-system synchronization

- SystemFlow<sup>®</sup> API & GUI with Signal Analyzer

- Complete documentation & lifetime support

Pentek, Inc., One Park Way, Upper Saddle River, New Jersey 07458 Phone: 201.818.5900 • Fax: 201.818.5904 • e-mail:info@pentek.com • www.pentek.com Woldwide Distribution & Support, Capyright © 2015 Pentek, Inc. Pentek, Talon and SystemFlow are trademarks of Pentek, Inc. Other trademarks are properties of their respective owners.

#### Model RTR 2729A 3.6 GS/sec Ultra Wideband RF/IF Rugged Portable Recorder

#### **Features**

- Designed to operate under conditions of shock & vibration

- Lightweight portable system in a rugged steel and aluminum chassis

- Shock- and vibration-resistant SSD storage performs well in vehicles, ships and aircraft

- 12-bit A/D, with 16- & 8-bit packing modes

- Capable of recording RF/IF frequencies to 1.75 GHz in single-channel mode;

2.8 GHz in dual-channel mode

- Real-time sustained recording rates of up to 4.0 GB/sec

- Up to 15.3 TB SSD storage

- Datasheet: pentek.com/go/2729Acal

#### Model RTV 2602 Serial FPDP Rackmount Value Recorder

#### Features

- System Flow

- Complete Serial FPDP record and playback system

- Lowest-cost entry into Serial FPDP

4U 19-inch industrial rackmount PC server chassis

- Real-time aggregate recording rates up to 400 MB/sec

- 4 TB of data storage to NTFS RAID disk array

- C-Callable API for integration of recorder into application

- Datasheet: <u>pentek.com/go/2602cal</u>

Pentek's rugged turn-key recorders are built and tested for fast, reliable and secure operation in your environment.

Call 201-818-5900 or go to www.pentek.com/go/edntalon for your FREE High-Speed Recording Systems Handbook and Talon Recording Systems Catalog.

## **SPONSORED ARTICLE: MEASUREMENT TECHNOLOGY**

#### THREE WAYS TO REDUCE UNCERTAINTY AND IMPROVE NOISE FIGURE MEASUREMENTS

#### Cherisa Kmetovicz, Keysight Technologies

**N**oise figure (NF) is a key parameter in the performance of RF receivers and systems. It measures the degradation in the signal-to-noise ratio (SNR) as a signal passes through the device under test (DUT). A receiver with a low noise figure has the capability to detect low-amplitude signals, and this directly correlates to improved bit error rate (BER) in a digital communications system.

The process of reducing noise figure starts with a solid understanding of the uncertainties in the receiver—its components and subsystems—and the test setup. Quantifying those uncertainties depends on flexible tools that provide accurate, reliable results.

#### Use an NF uncertainty calculator

The calculation of uncertainty can be complex and time-consuming, but it becomes simpler and faster with the many calculators available. The right choice depends on the chosen technique, and the most common choice is the Y-factor method. This uses two pieces of equipment: a calibrated noise source to provide a stimulus to the DUT input and a signal analyzer to serve as a calibrated receiver that measures the DUT's output noise.

The noise source is specified with an excess noise ratio (ENR) that characterizes the on and off noise power as a function of frequency. Because ENR uncertainty is a main contributor to overall NF uncertainty, it is included in the NF calculation. Other contributors include mismatch, gain linearity and the analyzer's own noise figure.

Table 1 illustrates the contributors to uncertainty for a low-noise 6 GHz amplifier with a 3 dB NF, 26 dB gain and a voltage standing wave ratio

| Contributor           | Percentage of total uncertainty |

|-----------------------|---------------------------------|

| ENR uncertainty       | 88%                             |

| Mismatch              | 12%                             |

| Gain linearity        | < 1%                            |

| Analyzer noise figure | < 1%                            |

**Table 1.** Two factors dominate the NF measurement uncertainty for a 6 GHz low-noise amplifier.

(VSWR) of 1.5. The noise source had an ENR uncertainty of  $\pm 0.078$  dB and a VSWR of 1.05, and the main contributors to total measurement uncertainty were ENR uncertainty at 88 percent and mismatch at 12 percent.

|                                                                                                                                      |                                                       |                                                                   |          | Unce                                      | ertainty Cal | ulator                                    |                               |                | 5            | 2 ?      | Close   |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------|----------|-------------------------------------------|--------------|-------------------------------------------|-------------------------------|----------------|--------------|----------|---------|

| Automate settings from DUT setup and measurement results                                                                             |                                                       | On                                                                |          |                                           | Update       | at currer                                 | at current CF 10.00000000 GHz |                |              |          |         |

|                                                                                                                                      |                                                       |                                                                   | _        |                                           |              |                                           | Update                        | at select      | ed frequency | 1.50500  | 0000 G  |

| OUT: Amplifier<br>NS: Auto                                                                                                           | Freq: 10.000 GH;                                      | Ext Preamp:<br>Instrument: A                                      |          | Freq: 10                                  | 000 GHz      | Noise                                     | Figure Uncertainty.           | 2 <del>0</del> |              |          |         |

|                                                                                                                                      |                                                       | Spec St                                                           | yle      | Distribu                                  | ution        |                                           | User Cal                      |                |              | ±0.122   | B       |

| DUT NF (dB)<br>DUT Gain (dB)<br>DUT In Match**                                                                                       | 3.550 dB<br>25.073 dB<br>1.500                        | Fixed*<br>Fixed*                                                  |          | Fixed                                     |              |                                           | Internal Cal                  |                |              | ±0.123   | зB      |

| OUT IN Match**                                                                                                                       | 0.240                                                 | Fixed<br>Fixed                                                    |          | Fixed                                     |              |                                           | Uncalibrated                  |                |              | ±0.138   | B       |

| NS ENR Uncert (dB)<br>NS Match**                                                                                                     | 0.106 dB<br>0.058                                     | 95th %ile'<br>Maximum                                             |          | Gaussia<br>Rayleigt                       |              | Sweep                                     | Uncertainty                   |                |              |          |         |

| nst NF (dB)<br>nst NF Uncert (dB)<br>nst Gain Uncert (dB)<br>nst Match**<br>nst NFE Impr (dB)                                        | 9.000 dB<br>0.025 dB<br>0.223 dB<br>1.690<br>9.000 dB | Fixed*<br>Fixed*<br>Fixed*<br>95th %ile<br>95th %ile*             |          | Gaussia<br>Gaussia<br>Rayleigt<br>Gaussia |              | Log<br>0.153<br>0.149<br>0.149            |                               |                |              |          |         |

| Ext PA NF (dB)<br>Ext PA Gain (dB)<br>Ext PA Match**<br>Ext PA NFE Impr (dB)<br>Fixed value, not editable<br>* May be entered as Ret |                                                       | Fixed*<br>Fixed*<br>Fixed<br>95th %ile*<br>SWR or Reft Coefficier |          | Fixed<br>Gaussia                          | in*          | 0.142<br>0.138<br>0.134<br>0.130<br>0.130 |                               |                |              |          | Unca    |

| Sweep<br>Parameter                                                                                                                   | Lower Upper                                           | Points t                                                          | User Cal | Int Cal                                   | Uncal        | 0.123                                     | 3                             |                |              | _        | Ugat Ca |

|                                                                                                                                      | 1.775 5.324                                           |                                                                   | On       | On                                        | On           |                                           | 1.77480483055115              |                |              | 5.324414 | 916534  |

**Figure 1.** As implemented in the NF application, graphical and informational results are presented on the screen of the EXA signal analyzer.

## **SPONSORED ARTICLE: MEASUREMENT TECHNOLOGY**

| Noise source             | Noise source ENR uncertainty | Noise source VSWR | DUT NF uncertainty |

|--------------------------|------------------------------|-------------------|--------------------|

| Smart noise source (SNS) | ±0.087 dB                    | 1.05              | ±0.112 dB          |

| Typical noise source     | ±0.180 dB                    | 1.25              | ±0.213 dB          |

### **Table 2.** A smart noise source provides much less measurement uncertainty.

Adding up the components produced an uncertainty of  $\pm 0.112$  dB. This implies that an amplifier with a 3 dB noise figure would yield a measured value between 2.888 dB and 3.112 dB.

The fastest way to calculate uncertainty is to use a signal analyzer equipped with an NF measurement application. One example is the Keysight EXA X-Series signal analyzer (N9010B) and the N9069C noise figure application, which provides one-button operation and includes a built-in uncertainty calculator.

For the active measurement, the calculator reports total NF uncertainty on the instrument display. For example, the uncertainty calculator screen reports total measurement uncertainty along with a graph of uncertainty versus a swept parameter (e.g., DUT NF, gain or match).

#### Select a noise source with low uncertainty

Because ENR uncertainty has the largest effect on total measurement accuracy, it's important to use a noise source that has the lowest uncertainty for a specific application. One example is a Keysight SNS Series smart noise source, which automatically downloads electronically stored calibration data to the analyzer. It also automatically measures its own temperature so compensation can be applied to the calibration data. These noise sources provide less uncertainty than can be obtained with most standard noise sources. Table 2 provides a comparison.

#### Use a smart preamplifier

Adding a preamplifier to the test setup will improve the NF performance of the signal analyzer. The preamp can be either internal to the analyzer's signal path or an external unit that is inserted between the DUT output and the analyzer input (Figure 2).

External smart preamplifiers automatically download calibration information to the analyzer via USB and improve NF performance. Keysight's

**Figure 2.** Keysight instruments, applications and accessories work together to provide accurate, reliable NF measurements.

smart preamps provide gain correction with temperature compensation, and are also optimized to flatten the analyzer's frequency response and thereby reduce measurement uncertainty.

#### Conclusion

A robust solution set for noise figure measurements—instruments, applications, and accessories—simplifies the process of optimizing test setups and identifying unwanted sources of noise. The use of a one-button measurement application, a built-in uncertainty calculator, a low-uncertainty noise source, and a smart preamp will accelerate the process and improve measurement results.

**Download PDF of Article**

## **SOC DESIGN-FOR-TEST**

#### **REDUCING TEST TIME AND COSTS WITH NEW COMPRESSION TECHNOLOGY**

By Mike Vachon, Software Engineering Group Director, Cadence

Very working chip that comes off a production line spends part of its time on automated test equipment (ATE), where its memories, chip I/O interfaces, analogue circuitry, and digital logic are carefully examined. Typically encompassing 10-50% of total test time, testing of digital logic can represent a significant portion of overall product cost.

All told, testing is a costly, yet critical, part of the overall chip development process, with the industry spending roughly \$4 billion annually on ATE. And as chip designs continue to grow in size and complexity, particularly at advanced nodes, test costs will only continue to go up.

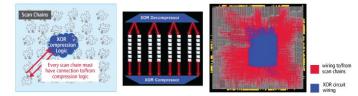

We've seen various cost-reducing test technologies rolled out by the Design for Test (DFT) community over the years, but nothing deserving the description of a breakthrough in the last 15 to 20 years. Today, XOR-based test compression, typically providing compression ratios of 50- to 100-fold, remains the most widely used. XOR compression reduces test time by partitioning registers in a design into more scan chains than there are scan pins on the chip to connect to the ATE.

At process geometries of 16nm/14nm, however, SoC designers are finding that they need to go beyond 100X compression in their scan vectors in order to control test cost and avoid having to spend money buying additional testers. Clearly, the market is ready for a new way to minimise test costs.

Figure 1. Wiring overhead associated with compression logic.

## Limitations of traditional XOR compression

As the ratio between the number of scan chains and the number of scan pins increases in a traditional XOR compression architecture, the length of each scan chain decreases, resulting in fewer clock cycles to shift-in each test pattern. For a constant pattern count, fewer shift clock cycles per pattern requires less total test time on the ATE – hence the test cost savings advantage.

Fewer clock cycles per pattern also means

Download PDF of Article fewer bits of information in each pattern to control register values and detect faults. In this scenario, a higher compression ratio becomes problematic. Should the compression ratio become too high, the achievable fault coverage drops because some faults will need more register values to be controlled than there are bits in a test pattern. Even if fault coverage can be maintained, as the compression ratio goes up, the number of patterns needed to maintain this coverage increases rapidly because it becomes more difficult to pack the detection of multiple faults into a single pattern. Ultimately, increasing the compression ratio results in a diminishing benefit on total test time. In addition, a higher compression ratio results in a substantial impact on the physical implementation of a chip-after all, every scan chain has to be connected to and from the XOR compression logic (as shown in Figure 1).

At a typical compression ratio of 100X, the average impact on total chip wiring resources of an XOR codec across a range of common digital components is in the range of 3-5%. What if you attempted to increase the compression ratio to 400X, particularly to meet the test needs of advanced-node designs? ... article continuation: click for pdf

#### Find SoC Design for test on EETsearch

## **Eye on Standards**

#### IT'S NOT JITTER, IT'S NOISE

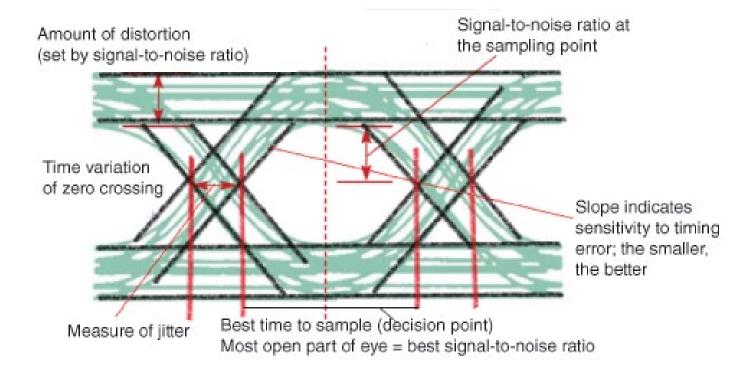

An oscilloscope draws a two-dimensional view of a signal – voltage versus time. In this column, let's ponder noise in these two dimensions.

When we look at a digital signal on a oscilloscope, the only noise we care about is noise that causes errors. In high-data-rate signals, the vast majority of errors occur when the timing of a logic transition fluctuates across the sampling point. That sampling point should be close to the centre of the eye. For a differential signal, it's right around (t, V) = (n+1/2T, 0), where n is an integer, and T is the bit period.

If transitions had zero rise/fall time, jitter caused by phase noise would be the sole culprit. But voltage noise shifts edge timing, too.

Consider the rising edge of a 0-to-1 transition. If, for example, voltage noise pushes the edge down, then the time position at V=0 shifts to the right. If the rise time and voltage noise are large enough, the edge shifts past the sampling point, and what should have been a 1 is mistaken for a 0.

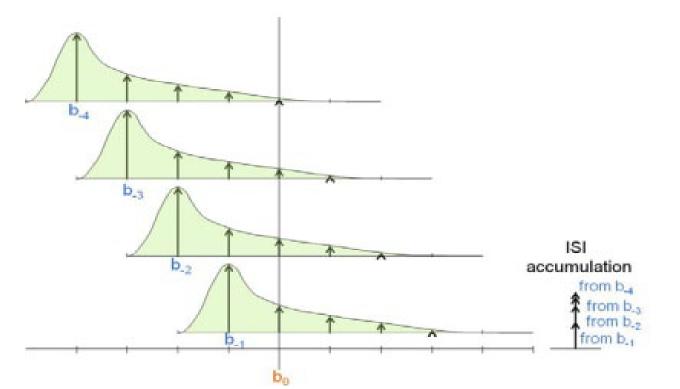

In high-speed serial systems, the channel is the dominant cause of eye closure. The channel acts like an attenuating low-pass filter. Rise/

#### **BY RANSOM STEPHENS**

fall times increase as higher-frequency components are damped out. The effect is called intersymbol interference (ISI), because the shape of a particular bit in the waveform is affected by the frequency content of bits that surround it. For example, a sequence of alternating ones and zeros has higher-frequency content then a long string of identical bits.

The combination of more gentle edges and

reduced peak-to-peak voltage causes errors in two ways. First, the gentle-sloping edge of a transition might pass right by the sampling point. Second, a transition may never be higher or lower than the sampling-point voltage. The amplitude of a 1-to-0 transition that follows a long string of identical bits may not drop below the sampling point through the entire bit period.

## **Eye on Standards**

A more interesting point (and, as 100-Gigabit Ethernet emerges, an increasingly relevant one) is crosstalk-induced jitter. Crosstalk is electromagnetic interference (EMI) generated by logic transitions of one signal, the aggressor, and picked up on the trace of another, the victim. The magnitude of the pickup depends on the victim-aggressor mutual inductance.

Both ISI and crosstalk cause jitter, but they are voltage noise, not timing noise.

Of course, equalisation was invented to defeat ISI. It's easy to amplify the high-frequency signal components that ISI damps out. You can do it at the transmitter with de-emphasis or at the receiver with a continuous time linear equaliser (CTLE), in either analogue or digital form, or with a linear feed forward equaliser (FFE).

It's worse for crosstalk, though. Simple equalisation techniques can open eyes closed by ISI, but to a receiver, crosstalk looks like randomly occurring blasts of noise. No simple, linear equalisation technique can reduce the effects of crosstalk. Depending on the relationship between the underlying clocks of the victim and the aggressor, decision feedback equalisers (DFEs) can help.

In both cases, to understand how both voltage and timing noise affect your system, don't overlook noise analysis in your headlong rush to jitter analysis. Most advanced oscilloscope jitter analysis software includes noise analysis. Another way is to expand the two-dimensional V(t) analysis of an oscilloscope to three dimensions with a bit error rate (BER) tester or a BERTscope and look at BER(t, V), also known as the BER contour.

#### **PAYING DOWN TECHNICAL DEBT**

By John Paliotta, Vector Software

n last month's edition, John Paliotta introduced the concept of technical debt; the burden we impose on systems in the form of latent defects introduced during system architecture, system design, or system development. In this second part of the discussion he looks at how – like all who have over-indulged in tempting credit – we can begin to pay back the debt and, especially, to prioritise which parts of the debt mountain to attack.

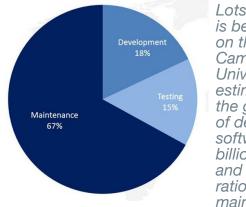

Technical Debt is a great metaphor for the latent bugs and ugliness that exists in all of our code bases. There have been lots of advances in software development processes over the last 30 years, but the quantity of software being developed has far outpaced our ability to build quality software efficiently.

Cambridge University estimates that the global cost of debugging software is \$312 billion annually. Software publishers are under constant pressure to release new products and new features quickly, which often causes a conflict between quality and time-to-market, as release cycles shrink from years to weeks to days.

Lots of money is being spent on the problem; Cambridge University estimates that the global cost of debugging software is \$312 billion annually; and an accepted ratio is that maintenance

costs are generally double the original development and testing costs.

In this article we'll discuss practical ideas for reducing technical debt in our legacy code bases; which will increase quality, reduce maintenance costs, and allow us to deliver new functionality to our customers, faster.

#### How did we get here?

Technical debt is not new, nor is it all bad. We rarely have the time to build the perfect product, or the perfect software application: there are always trade-offs.

Software is very malleable, it is easy to change, which makes it easy to break. Most software exists in a constant state of flux; you

pdf

Download PDF of Article start with a nice clean design, but that design gets corrupted as changes are made to fix bugs and implement new features. Without constant vigilance and refactoring, software applications get ugly over time.

Years ago when software applications were much smaller, the solution to ugly applications was a complete re-write. When the average application was only 50,000 lines of code – it was easy enough – or, at least, feasible – to throw them away and create a new implementation.

With modern application sizes in the millions of lines of code this is no longer an option, incremental improvement is the only option.

#### Understand the problem

To understand where technical debt may be building up, it is important to look at metrics.

The top four causes of technical debt are: poor architecture, overly complex code, inadequate testing, and lack of documentation. So the first step is to capture key metrics related to these issues: cyclomatic complexity, source code coverage, and comment density. ...article continues, click for pdf

Find Technical debt on EETsearch

## **RF POWER DEVICES**

#### **USING COMMUNICATIONS SEMICONDUCTORS TO COOK BETTER BURGERS**

#### By Robin Wesson, Ampleon

The ubiquitous microwave oven is about to be revolutionised by the application of solid-state RF electronics and signal-processing techniques borrowed from the communications industry and applied to what, for many households, will be their last vacuumtube-based appliance.

Improvements in the power output and efficiency of solidstate RF amplifiers mean they can now replace the resonant-cavity magnetrons that have been used in microwave ovens since they were launched 70 years ago. This will bring designers new ways to control how these ovens cook our food, and provide consumers with better burgers and "perkier pancakes". The same enhanced control of heating, and precision of results, is also available to designers of systems that use microwave heating as part of an industrial or manufacturing process.

How is this possible? After decades of development, magnetrons generate high-power RF signals with good efficiency at relatively low cost. However, the output frequency of this valve technology varies, its performance changes with temperature, and it is not possible to control its amplitude or phase accurately.

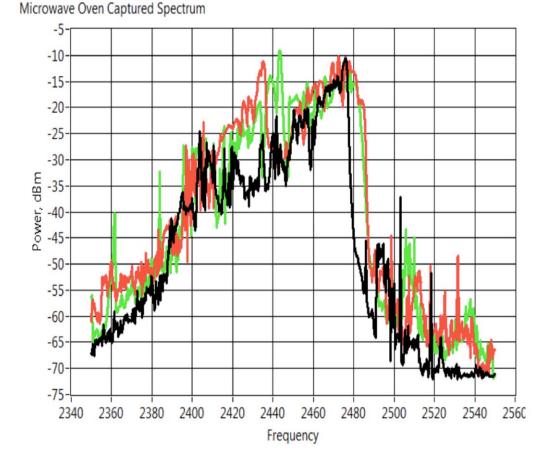

You can see the result in Figure 1, which shows an oven heating the same load for 30s, three times over. It's hard to deliver consistent cooking on the basis of such variability.

There are two further issues with microwave cooking, regardless of the RF source used. The first is that the way that RF energy is absorbed depends on its frequency and the dielectric properties of the food. This means that, for consumer microwave ovens operating around 2450 MHz, food is only directly heated to a depth

**Figure 1.** Magnetron spectral emissions in microwave oven operation – 3 traces of 30 seconds captured from the same oven with the same load (Source: Ampleon)

## **RF POWER DEVICES**

of a couple of centimetres. The second issue is that microwave energy from the source interacts with the cavity to set up standing waves with local energy maxima and minima, which in turn create hot and cold spots in the food being heated.

The fact that the standard measure of a microwave's utility is its ability to heat a litre of water has done little to encourage designers to develop ovens that work well on real food.

#### The innovation opportunity

The communications industry has been developing and using high-power RF components for decades. Communications system designers also face issues, such as delivering enough signal energy to users in complex multipath environments, which are surprisingly similar to those of a microwave oven designer – although the scale is different.

So what techniques can microwave oven designers borrow from their communications industry colleagues, and what opportunities for innovation would they bring? Let's examine a few of these.

#### **Power control**

The amount of energy delivered to the food in today's microwaves is controlled by turning the magnetron on and off - a basic form of pulsewidth modulation (PWM). The switching rate is limited by the time it takes for the magnetron to reach its operational temperature, which can result in poor cooking results due to thermal cycling at the edges of some foods.

Solid-state systems can handle PWM control with periods measured in microseconds, not the seconds necessary for magnetrons, making it possible to deliver energy in a more linear fashion. In effect, the flexibility of a solid-state power delivery gives microwave users the same control of power delivery that we take for granted from an electric oven or gas grill. The solidstate approach offers one more advantage - variations in the power and gain of the source can be corrected with a closed-loop control system, improving repeatability. The article continues, considering the application of feedback and frequency/phase control- click for pdf.

Stay informed on what's going on in the electronics industry

Download PDF of Article

Find RF Power Devices on EETsearch

## **EDA: SYNTHESIS**

#### **NEW GENERATION OF PHYSICAL RTL SYNTHESIS IMPROVES QUALITY-OF-RESULTS**

By Arvind Narayanan, Mentor Graphics

The quality of the netlist generated during RTL synthesis has an enormous impact on the rest of the physical design flow. For teams designing large SoCs at advanced nodes, it is more important than ever to come out of RTL synthesis with predictable timing and congestion estimates, DFT, and even a floorplan with good pin placements and feedthroughs. The quality of the netlist coming out of RTL synthesis has a big impact on the speed and predictability of the backend physical implementation and signoff.

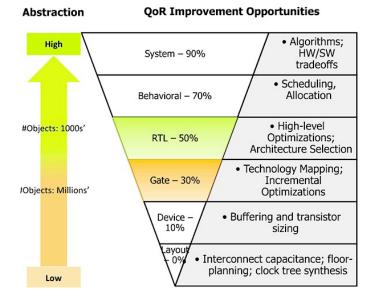

What does quality of the netlist mean, and what are the bottlenecks of getting a good quality netlist for physical implementation? One barrier to better quality of results (QoR) from synthesis is when the synthesis tool optimises the design after generating gates from the RTL. For the best quality, designers need a highcapacity, physically-aware logic synthesis tool that optimises at a higher level of abstraction, not at the gate level. There are far more opportunities for QoR improvements when synthesis optimisation is performed at the RTL level.

However, there is a lack of physical information at the RTL level. Resorting to wire load models causes sub-optimal QoR metrics for

**Figure 1.** Optimising at the RTL level offers more room for QoR improvement than gatelevel optimisation, in addition to enabling higher capacity and faster runtimes.

timing and congestion. The answer is to perform placement before synthesis so that highlevel optimisation can be performed at the RTL level instead of the gate level, as with traditional synthesis tools. The new RTL synthesis tool should be able to divide the RTL into virtual placeable partitions and then refine those down into actual library cells so that physical placement information is available at all times. A detailed netlist of each RTL partition should be used to accurately time the design. Each partition should be optimised and implemented as placed gates and if needed, the RTL should be repartitioned until all top-level design specifications are met. The placement and timing information should be dynamically updated with every optimisation transform. This will result in a very tight correlation between RTL synthesis and place and route for timing and congestion.

The second barrier to QoR is that restricted tool capacity forces designers to break down their chips into smaller blocks for synthesis, and then re-stitch during physical design implementation. Breaking the design into blocks that don't correspond to the physical hierarchy is a recipe for disaster as it is very difficult to get a good partition, and hard to budget timing constraints across the blocks. The problem with this block-level synthesis approach manifests as endless iterations when assumptions made in the synthesis tool, which can only see a single block at a time, are invalidated by the physical design tool when all the blocks are considered as a group. The design that emerges from place and route no longer satis-

## **EDA: SYNTHESIS**

fies its constraints resulting in a mis-correlation between front- end and back-end design flows. Particularly for large designs, RTL and physical engineers should look for a tool with the capacity to perform true chip-level synthesis and floorplanning.

A side benefit of having high-quality physical RTL output is that it makes the entire design flow more predictable with shorter design cycles. Optimising at a higher level reduces RTL synthesis runtime, gives faster design convergence and cuts the time-consuming iterations. Using a high-level RTL physical synthesis solution with the capacity to handle 100+ million gate designs will deliver an enormous increase in productivity.

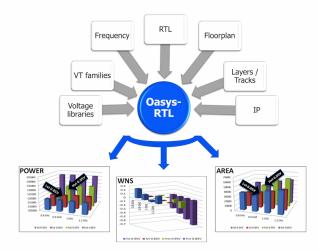

The third barrier to QoR is the general lack of robust what-if analysis during RTL synthesis. With a newer-generation RTL synthesis tool, designers can cross-probe between physical and RTL databases to debug timing or congestion problems. They can also perform parallel explorations of different design metrics, for example, varying the weight of power, performance, timing, DFT, and area to find the best alternative for implementation. The tool should be able to perform multiple fast synthesis runs with the different constraints for voltage, clock speed, and library, and gives the results in a comprehensive summary format.

**Figure 2.** Fast design-space exploration enables the designer to check and modify the design to meet timing, power, area, congestion, and DFT specifications.

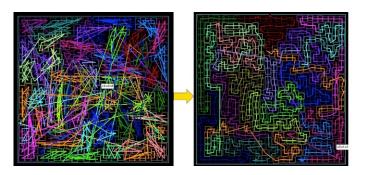

A final thought on design quality is the importance of chip-level DFT. Testability is increasingly difficult and undeniably important. Selecting DFT friendly architectures early and performing scan insertion at the full-chip RTL level helps reduce test time and limits the impact of test logic on die size. Physical RTL synthesis takes into account the physical location of flops when creating scan chains. Working at the chip level is better than working at the block level and then manually hooking up the sub-chains. Performing scan insertion during synthesis also lets potential test problems be debugged early in the design cycle.

**Figure 3.** The screen shot on the left shows a design in which the scan chains have not been ordered with their physical placement taken into account. The screen shot on the right shows the same design re-implemented using the physical placement information. Each scan chain is a different colour so the advantage in terms of routing is clear.

Good RTL synthesis is critical for improving the performance, power, and area challenges in today's large advanced-node SoCs. A next-generation physical RTL synthesis tool must have higher capacity, faster runtimes, and better QoR than what's available in traditional synthesis solutions. Learn more about the concepts described here in the [Mentor Graphics] Oasys physical RTL synthesis white paper.

#### **ATTAINING FUNCTIONAL SAFETY IN MCU-BASED DESIGNS**

By Hoiman Low, Texas Instruments

n the 1980s, the use of programmable electronic components such as microcontrollers (MCUs) and microprocessors in industrial control systems began to grow. The International Electrotechnical Commission (IEC) set up study groups to examine the functional safety of electronic programmable systems and to develop guidelines for the development of safe systems. Since then, compliance to functional safety standards has become a customer-influenced requirement for end equipment developers in automotive and many industrial applications.

## Standards, certification, and the development process

The first standard intended to apply to a wide variety of industrial systems was the IEC 61508 first edition, "Functional safety of electrical/ electronic/programmable electronic safetyrelated systems," published in 1998. In 2011, the automotive functional safety standard ISO 26262 "Road vehicles — Functional safety" was published. The purpose of both standards is to establish requirements that reduce potential risk of physical injury and damage to the health of people due to product failure. They call for implementing a robust development process, performing upfront hazard and risk

| Standard  | System                      | Safety<br>Integrity                    | Architectural<br>Metric | Architectural<br>Requirement        | Failure<br>Rate   | Specific MCU self-test<br>requirements       |

|-----------|-----------------------------|----------------------------------------|-------------------------|-------------------------------------|-------------------|----------------------------------------------|

| IEC 61508 | Programmable<br>E/E systems | SIL – 1,2,3,4                          | SFF                     | HFT>0 for SIL 4                     | PFD, PFH          | No                                           |

| ISO 26262 | Automotive                  | ASIL – A, B,<br>C, D                   | SPFM / LFM              | No                                  | PMHF              | No                                           |

| EN 50129  | Railway                     | SIL- 1,2,3,4                           | N/A                     | Follow IEC<br>61508                 | THR               | CPU, Memory                                  |

| ISO 22201 | Elevator                    | SIL – 1,2,3                            | N/A                     | Dual channels<br>for SIL3           | N/A               | CPU, Memory, Interrupt,<br>Clock, I/O, Comm  |

| IEC 61800 | Drive                       | SIL – 1,2,3<br>SIL4 Apply<br>IEC 61508 | SFF                     | Dependent on<br>function            | PFH<br>(no PFD)   | No                                           |

| IEC 62061 | Machinery                   | SIL – 1,2,3<br>SIL4 Apply<br>IEC 61508 | SFF                     | Supports ISO<br>13849<br>categories | PFH <sub>D</sub>  | No                                           |

| IEC 61511 | Process<br>Automation       | SIL – 1,2,3<br>SIL4 Apply<br>IEC 61508 | SFF                     | See IEC 61508                       | PFDavg            | No                                           |

| ISO 13849 | Machinery                   | PL a,b,c,d,e                           | DCavg                   | CAT B,1,2,3,4                       | MTTF <sub>D</sub> | No                                           |

| IEC 60730 | Home<br>Appliances          | Class A, B, C                          | No                      | Yes (Class C)                       | No                | CPU, Memory, Interrupt,<br>Clock, I/O, Comms |

Figure 1. Safety standards.

### **EMBEDDED SYSTEM SAFETY**

analysis, and implementing product risk reduction in both hardware and software.

IEC 61508 and ISO 26262 share a common functional safety lifecycle and many of the same supporting processes. Many other industry safety standards leverage these two, typically following IEC 61508 for reference adding specific architectural and self-test requirements for each particular system. Fig. 1 shows a summary of the various functional safety standards and their relationship with IEC 61508.

For a design to claim compliance to IEC 61508 and ISO 26262 functional safety standards, there must be a functional safety assessment of the end equipment, including any functional-safety-critical components used in the design that claim to comply with these standards. The end equipment assessment must be independent of the design team, and the level of independence is defined by the applicable functional safety standards. The end equipment assessment can be performed by an independent workgroup within the end equipment company, for instance, or by an independent third party certification agency. Exida, various Technischer Überwachungs-Verein organisations (known as TÜV), and Underwriters Laboratories (UL) are among the authorities offering such services.

But achieving effectiveness is more than performing end-product functionality develop-

ment. End products must be developed using effective and necessary safety mechanism(s) to minimise the likelihood of failure occurring that would cause harm and include in the product built in mechanisms that facilitate a safe and predictable state when a product does fail.

#### Attaining safety certification